Software-defined Timing: Embedded Timing for Next-generation Communication Systems

Technical & Application Notes

Full programmable functionality is already a reality in today’s modern FPGA technology. This facilitates the rapid adoption of technologies such as software-defined radio or networking systems and their implementation in embedded platforms.

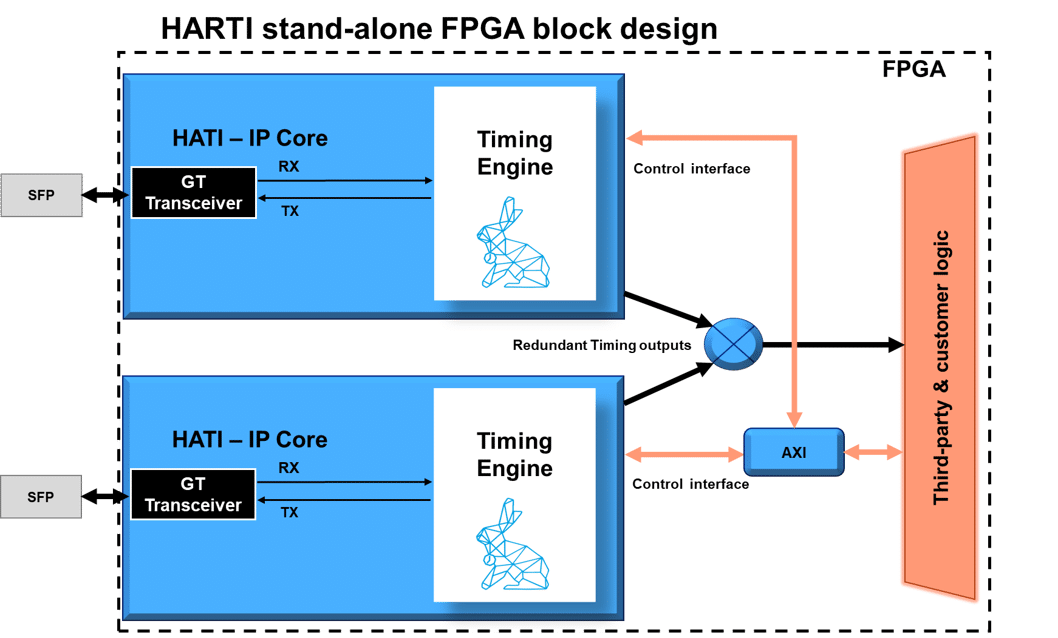

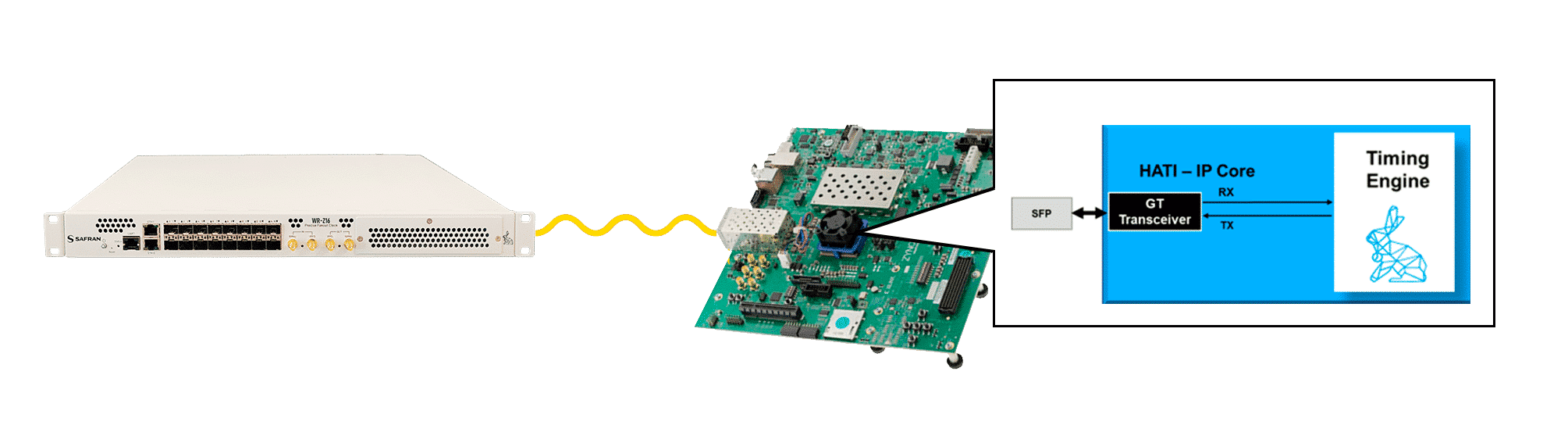

The next generation of timing solutions is based on the exploitation of the full programmability of FPGA towards the software-defined timing paradigm. HATI (High Accuracy Timing IP) core uses only FPGA devices resources with no external clocking circuitry required. HATI implements the White Rabbit protocol to provide sub-nanosecond timing transfer over Ethernet links on third-party enabled devices requiring only optical Ethernet interfaces. Below are the key design considerations, performance, design trade-offs and some key use cases.

Key features

-Time-transfer software defined solution using only built-in FPGA resources and an optical fiber Ethernet interface.

-Target applications: datacenters, fintech, telecommunications and industrial time transfer.

-External management and configuration interfaces allows configuration, calibration, reading IP status.

-FPGA families:Kintex7, Kintex7-US, Kintex-7US+, Virtex7 & Virtex7-US+, Zynq 7 & Zynq US+, Artix-US

-It enables time and frequency distribution with a sub nanosecond accuracy and picosecond level precision to the last hop through standard fiber optical fiber.

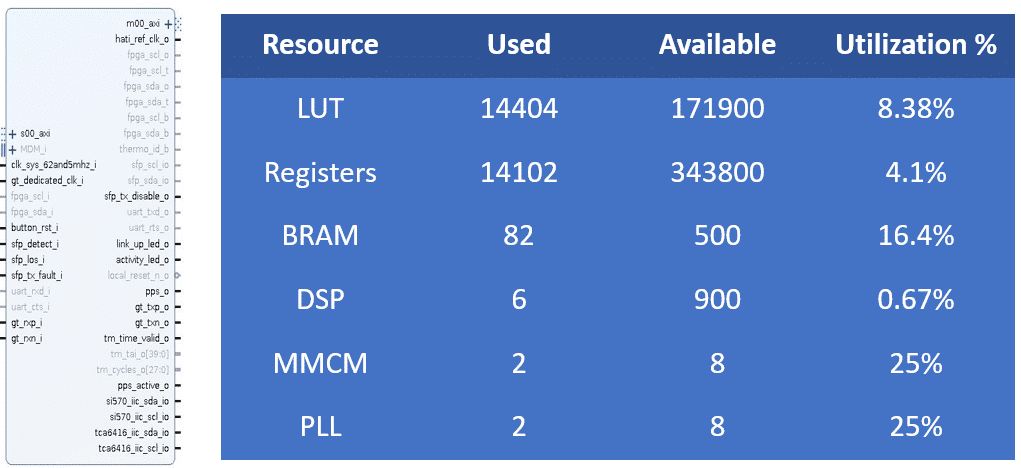

HATI FPGA interface and resources (Xilinx XC7Z035FFG900-2)

HATI reference design based on Xilinx ZCU102

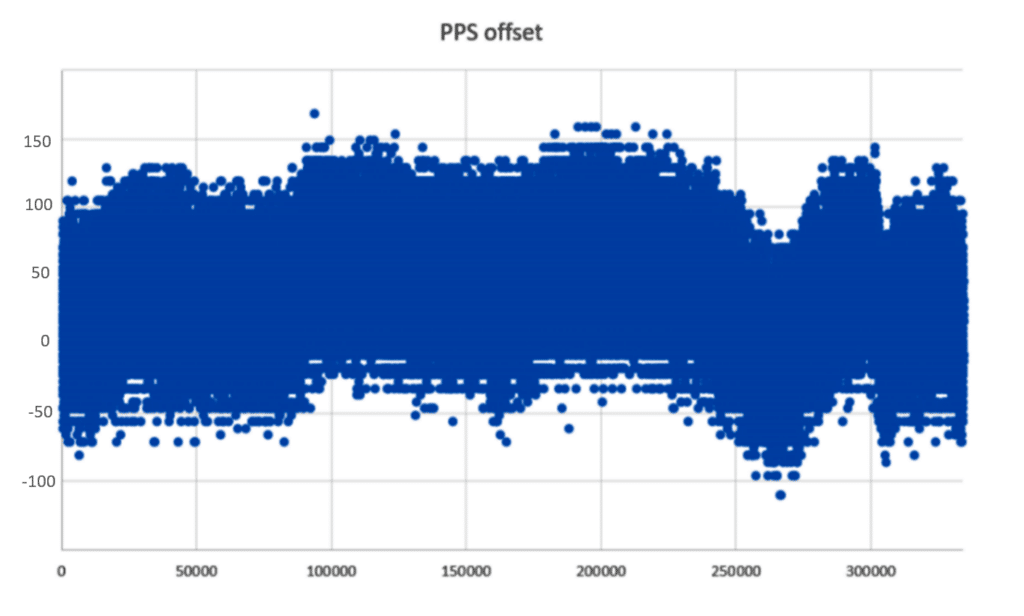

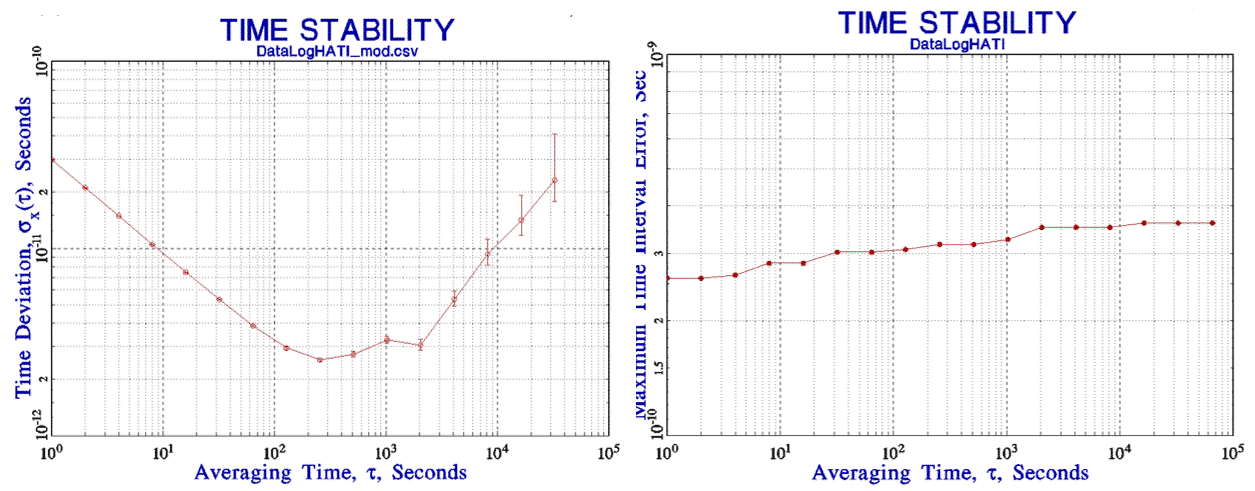

HATI MTIE and TDEV Results

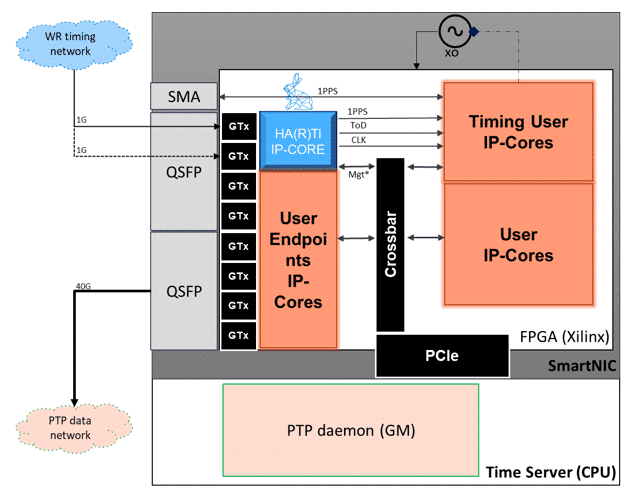

Use case example: HATI enabled Smart NIC