dBus-level timing board (TSync and TPRO/TSAT families) support assistance document

Note: This document contains both "Public Information" and "Internal Use Only Information" (do not release this document in its entirety to anyone outside of Orolia)

### **Table of Contents**

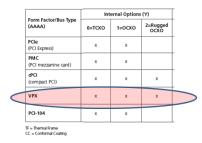

| TSYNC FAMILY OF BUS-LEVEL TIMING BOARDS                                        | 20     |

|--------------------------------------------------------------------------------|--------|

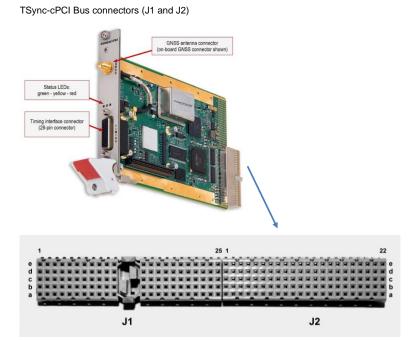

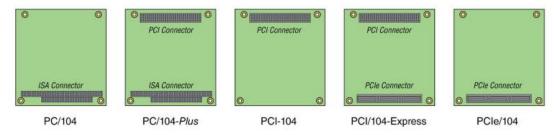

| Available TSync bus Connectors                                                 | 20     |

| TsyncE-PCIe (TSync-PCIe-002 and TSync-PCIe-012) boards with external           |        |

| GPS/GNSS receiver                                                              | 21     |

| Obsolete the PCIe-0x2 variants which have the Acutime external GPS             |        |

| antenna, except for Schneider Electric (special P/N)                           | 21     |

| Three (3) digit Model Number configuring scheme for TSyncs (TSync-xxxx -X      | (YZ) / |

| TSyncl/TSyncE                                                                  | 22     |

| TSync series discontinuance: Last Time Buy/TSync-PCIe replacements             | 24     |

| Lifecycle/end of life statement                                                | 25     |

| Timekeeper software with a TSync series timing board                           | 25     |

| Non-Spectracom "TSync" software program                                        | 25     |

| TSync-PTP (TSync-PCle-PTP boards) are now discontinued                         | 25     |

| MTBF for TSync boards                                                          | 25     |

| Agency Approvals/Compliance (TUV/UL/CE Declaration of                          |        |

| Conformity/EMC/EMI/ESD)                                                        | 25     |

| CE Approval/CE Declaration of Confirmity (DoC)                                 | 26     |

| Terms associated with TSync boards                                             | 26     |

| ISO 8 cleanroom requirements                                                   | 26     |

| GPS 1024 week rollover (such as in 2019)                                       | 27     |

| Conformal Coating (also "CC" in data sheet)                                    | 27     |

| Tin, lead and gold on TSync boards                                             | 27     |

| Conduction Cooling Thermal Frame (also "TF" in TSync datasheet)                | 27     |

| Onboard battery/Battery backed time (for sync to itself after every boot-up)   | 28     |

| Number of TSync boards that can be installed in a single PC/more than one T    |        |

| board installed                                                                | 28     |

| TSync Ancillary kits                                                           | 32     |

|                                                                                |        |

| TSYNC-PCIE TIMING BOARDS                                                       |        |

| TSync-PCle Shortcuts/Links                                                     | 37     |

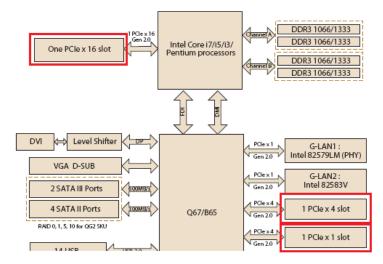

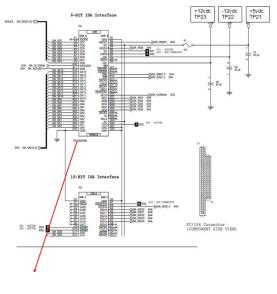

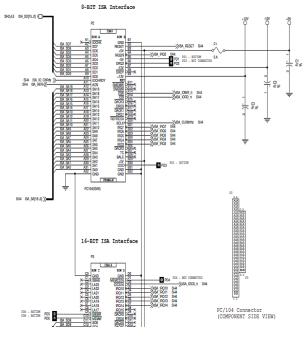

| HOST PCIe BUS interface                                                        | 37     |

| PICMG 1.3 (also known as SHB Express)                                          | . 38   |

| PCI to PCIe adapter (for installing a TSync board into a system with no availa |        |

| PCIe slots)                                                                    | 40     |

|                                                                                |        |

| National Instruments (NI) PXi-e chassis/ PXI Express                            | 40       |

|---------------------------------------------------------------------------------|----------|

| Host systems that have difficulty with TSync-PCIe board install                 | 40       |

| HARDWARE (Drawings, Specs and FAQs about the board)                             | 43       |

| EEPROM                                                                          | 43       |

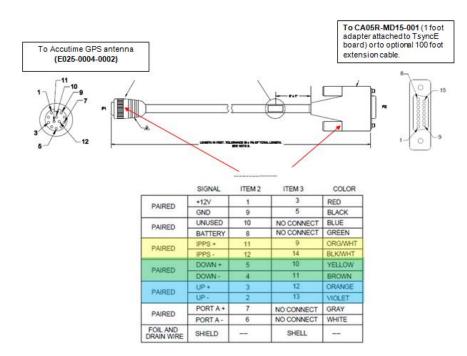

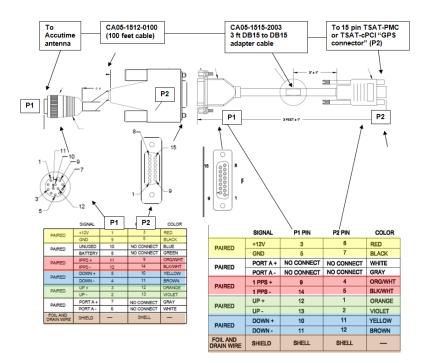

| TSync-PCle and Acutime Antennas for Invensys/Schneider Electric                 | 43       |

| Various packages associated with TSync-PCIe boards (such as for Invensys)       | 43<br>44 |

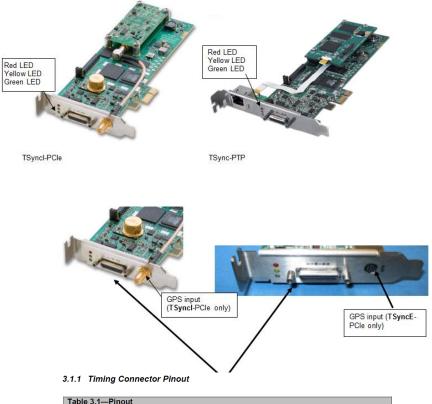

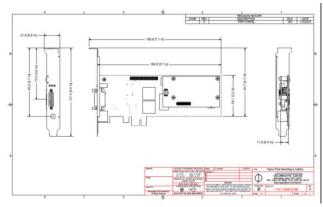

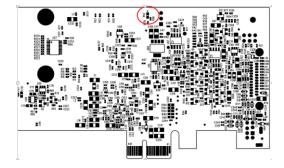

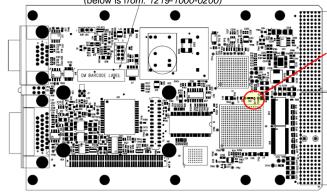

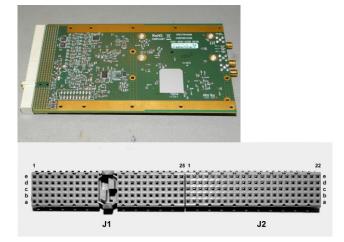

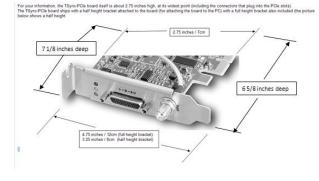

| Dimensional drawing of the TSync-PCle board                                     | 45       |

| PCle board generation (Gen 1, Gen 2, Gen 3, x1, x2, x16, etc) and Lanes         | 45<br>46 |

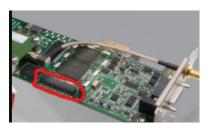

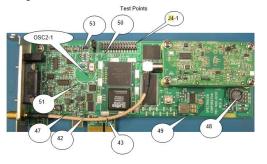

| Hardware changes to the TSync PCB boards                                        | 40       |

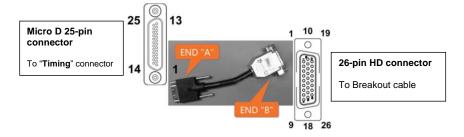

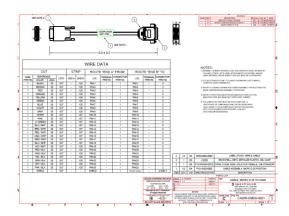

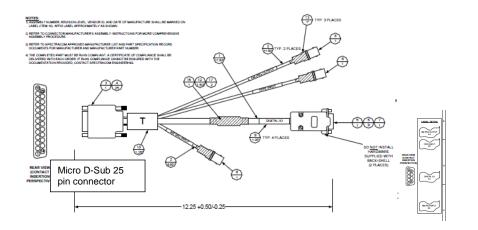

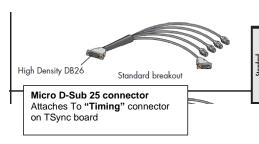

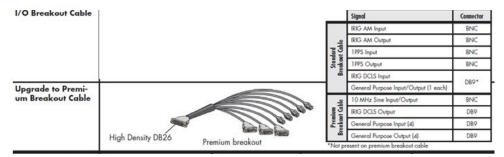

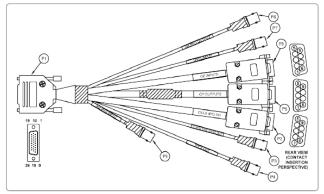

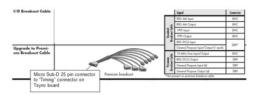

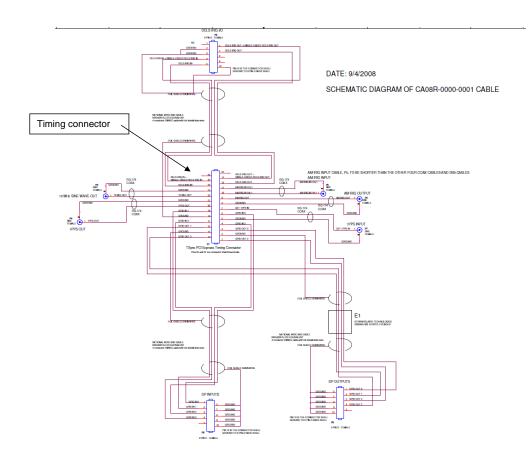

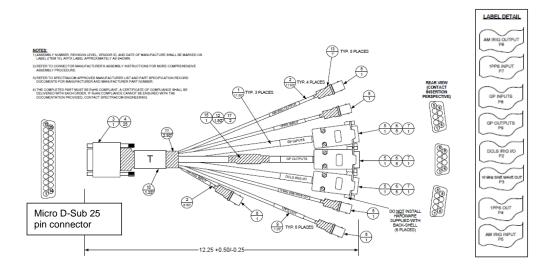

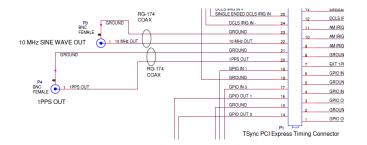

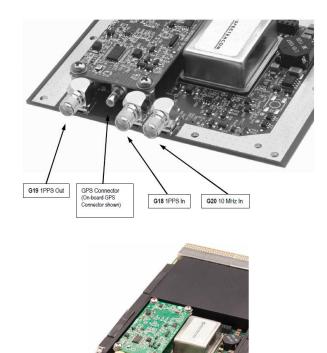

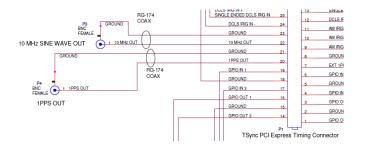

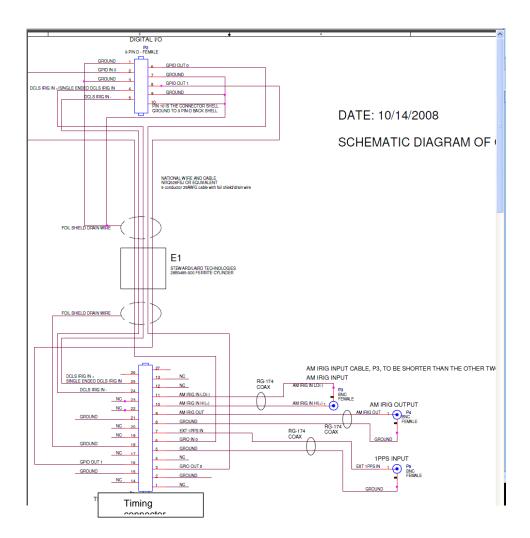

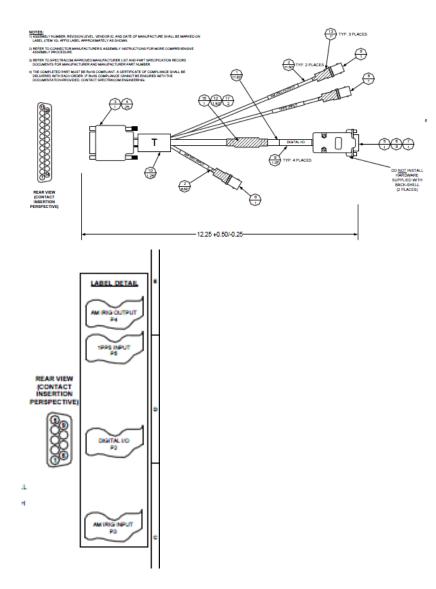

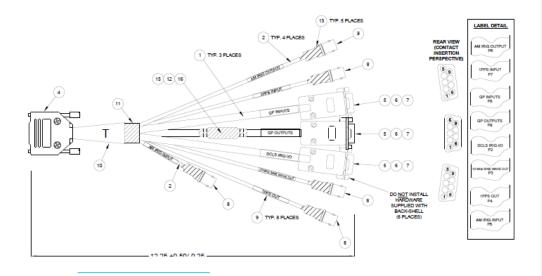

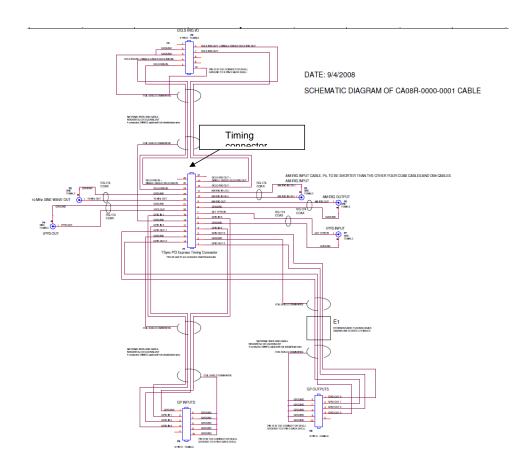

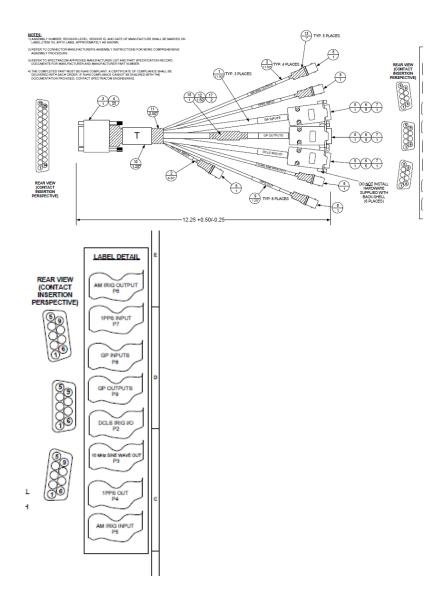

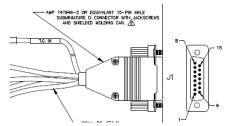

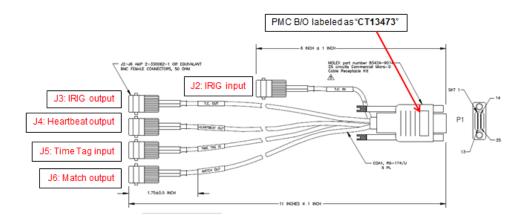

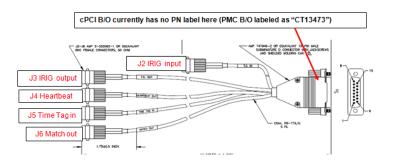

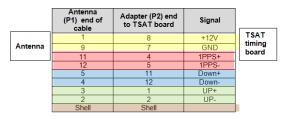

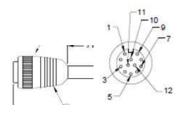

| Timing Connector for all TSync variants                                         | 50       |

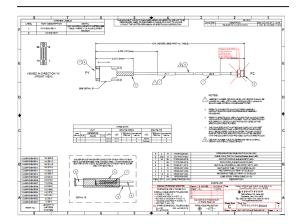

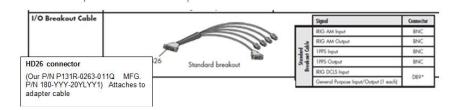

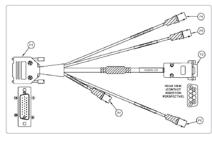

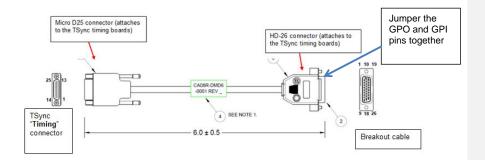

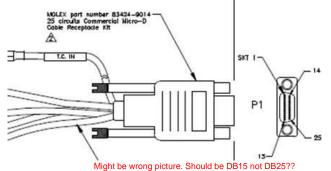

| Breakout cables/Interface cable for the "Timing" connector                      | 52       |

| Temperature specs for breakout cables                                           | 52       |

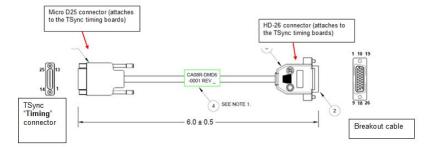

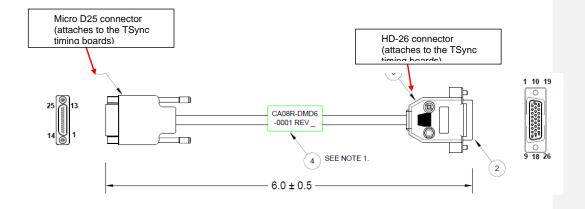

| CA08R-DMD6-0001: Timing Interface Adapter cable (for the newer DB25 connection) | -        |

| on standard and premium breakout cables)                                        | 52       |

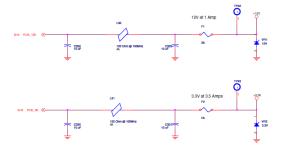

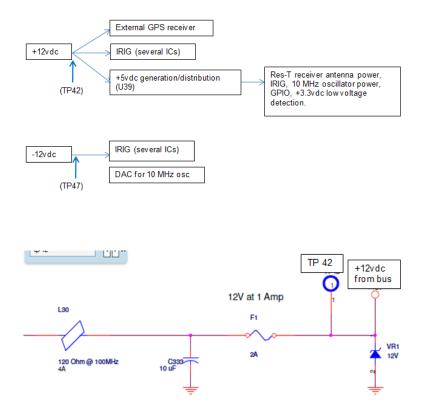

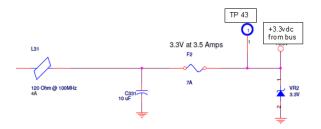

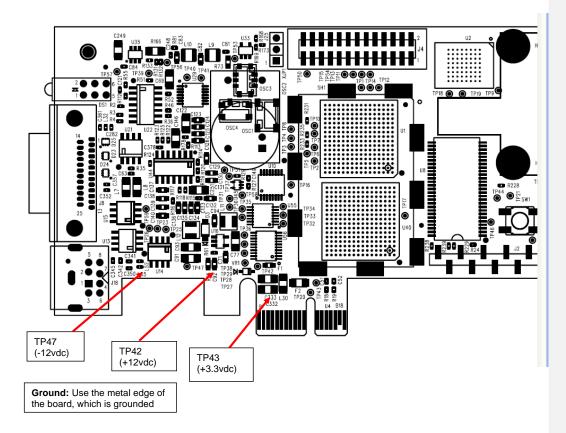

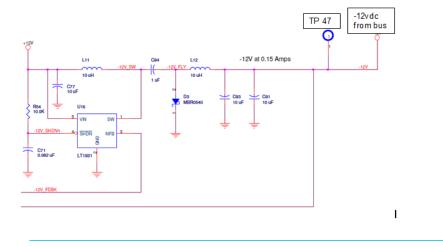

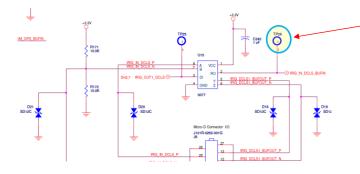

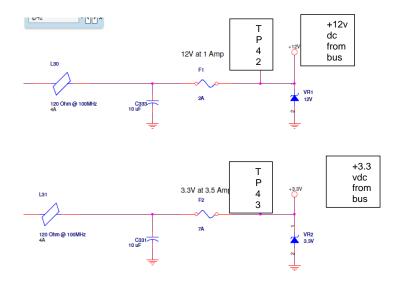

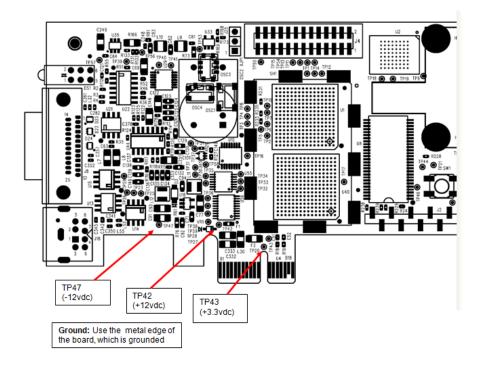

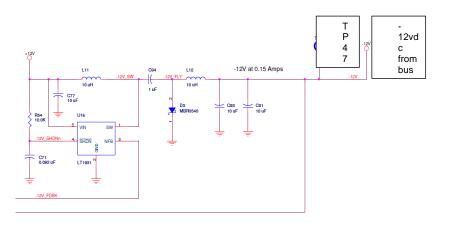

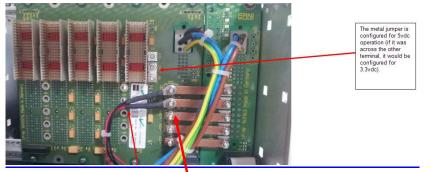

| Power (+3.3vdc +12vdc from PCI bus) +5vdc and -12vdc generation                 | 71       |

| Resetting the TSync-PCle board (Reset API call) and PTP module (if installed)   |          |

| Intermittent or constant system crashes/reboots occurring after a reset comm    |          |

| is issued.                                                                      | 76       |

| Specials                                                                        | 77       |

| Hardware status:                                                                | 77       |

| Interface issues with certain systems (such as HP and Dell computers)           | 80       |

| **Swapping out/Replacing an existing TPRO/TSAT board with a TSync-PCle b        |          |

|                                                                                 | 81       |

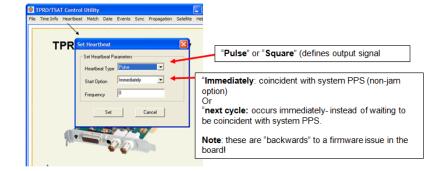

| **Heartbeat output                                                              | 82       |

| **HB1PPS Option                                                                 | 83       |

| **Desire to convert a TSyncl to a TsyncE / TsyncE to TSyncl                     | 84       |

| **Troubleshooting TSync boards/known issues                                     | 85       |

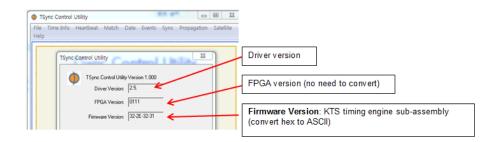

| FIRMWARE Versions                                                               | 85       |

| **Firmware version/updates - Firmware/FPGA/PTP module                           | 85       |

| TSync PTP Module firmware updates                                               | 88       |

| TSync-PCIe firmware updates/software issues                                     | 89       |

| Known issues with RES-SMT-GG receivers                                          | 90       |

| Firmware updates/driver updates                                                 | 93       |

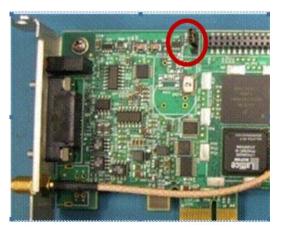

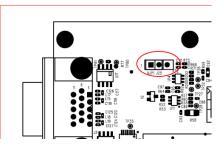

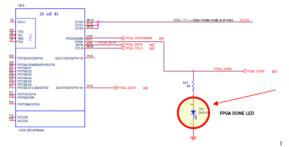

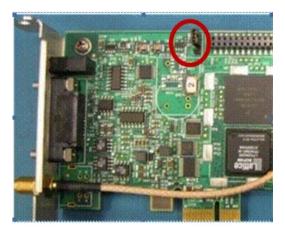

| TSync-PCIe FPGA program header (J25) / LED's (Programming and Status) / L       | _EDs     |

| upon reboot                                                                     | 94       |

| MEMORY/Certificate of Volatility (COV)/ Letter of Volatility (LOV)              | 99       |

| **System Memory allocation                                                      | 100      |

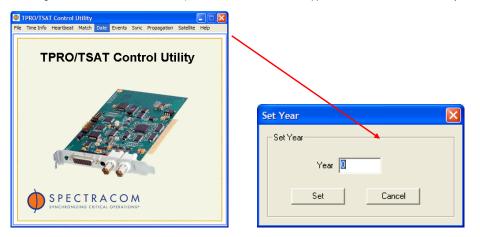

| **Limited NVRAM/most configs such as present year don't persist power cycl      | е        |

|                                                                                 | 101      |

| Temperature Sensor (firmware versions 3.4.7 and above)                          | 102      |

| Input references / Time Sync / Holdover                                         | 103      |

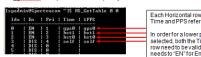

| **Input Reference Priority tables                                               | 103      |

|                                                                                 | 2        |

|                                                                                 |          |

| Defenence Maniford Defenence Otatus table (DO calle)                             | 400        |

|----------------------------------------------------------------------------------|------------|

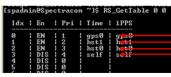

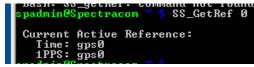

| Reference Monitor/ Reference Status table (RS_ calls)                            | 106        |

| Host reference and Self reference                                                | 108        |

| **Host Reference: TSync-PCle board without external inputs                       | 108        |

| API calls associated with Host Reference calls                                   | 109        |

| B) Self/Self Reference (Desire to sync the TSync board to itself)                | 112<br>114 |

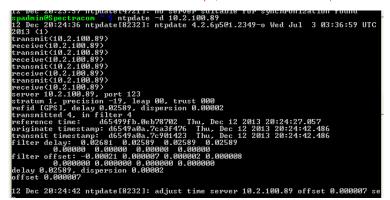

| **Desire to sync TSync board via NTP (indirectly)                                | 114        |

| **Desire to sync TSync board via an Endrun Praecis CDMA receiver (or other       |            |

| external references via ASCII data input)                                        | 114        |

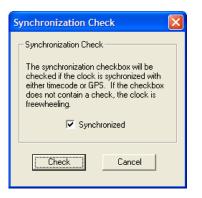

| **Time Sync and Holdover status/ green "sync" LED indication                     | 114        |

| **"Time" Input synchronization (PTP Slave, GPS input, IRIG input, Self, Hst 0)   | 117        |

| Timing board synchronization via IRIG playback from a tape                       | 118        |

| NMEA input (NMEA 0183) for synchronization                                       | 118        |

| **Selected reference/ Reference change notification                              | 120        |

| **PTP client software exhibiting excessive NTP offset and Jitter                 | 120        |

| GPS / Glonass / A-GPS                                                            | 127        |

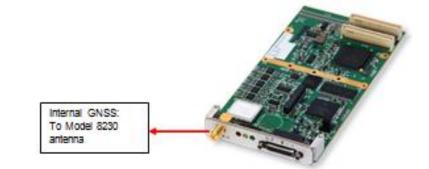

| Model 8230 GNSS antenna (8226 surge suppressor/8227 preamp)                      | 127        |

| **GPS Reference Component (GR_) Calls                                            | 130        |

| **TSYNC_DRV_CONNECTION_ERR with "GR" or "IR" calls                               | 133        |

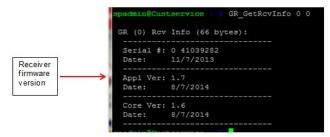

| **Determining type of receiver installed and receiver firmware version           | 134        |

| ****Google Part Numbers (receiver configurations for Google's TSync boards)      |            |

| **U-Blox M8T receiver (M8T)                                                      | 135        |

| ***Customer desire/need to replace Trimble Res-SMT receiver with UBIox M8T       | 135        |

| Resurvey: Need to reset the u-Blox receiver positon (if relocated while in       | 400        |

| Stationary mode)                                                                 | 138        |

| **Trimble Res-SMT-GG receiver                                                    | 139        |

| Resurvey: Need to reset the RES-SMT-GG receiver positon if relocated while i     |            |

| Stationary mode                                                                  | 139        |

| **Enabling /Disabling Constellations (GPS, Glonass and/or Galileo)               | .140       |

| **Desire to Blacklist (Mask/Unmask) a Satellite from being received by a Trimk   |            |

| RES-SMT-GG receiver                                                              | 142        |

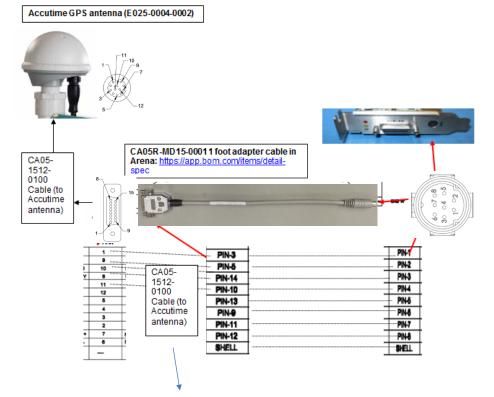

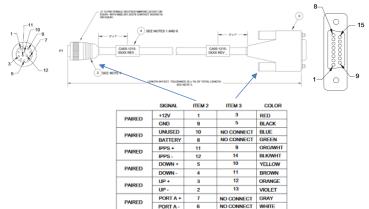

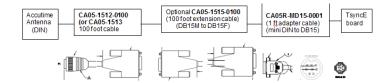

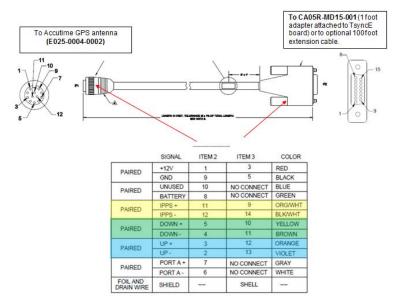

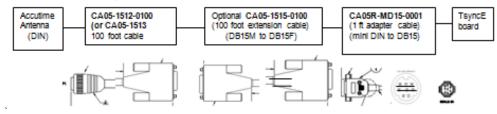

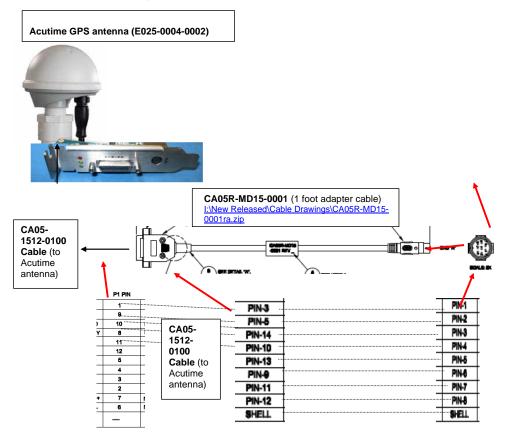

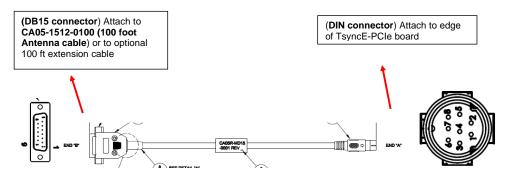

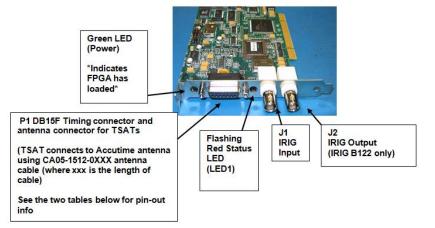

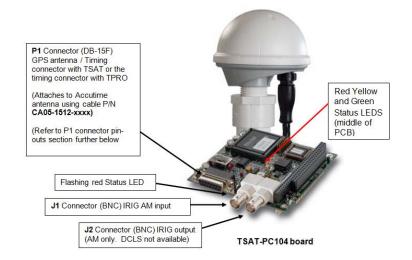

| **Acutime antennas ("TSyncE" / "TSync-PCIe-002 / TSync-PCIe-012")                | 143        |

| **Calls for setting the TSync-PCIe GPS receiver Mode/Dynamics code:              | 145        |

| Degradation of timing/positional accuracies in mobile mode (Continuous mod       |            |

|                                                                                  | 147        |

| Error log entries for GPS                                                        | 148        |

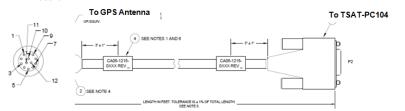

| Antenna cable delay/1PPS offset.                                                 | 148        |

| GR_GetFixData 0 0 response (GPS PDOP/HDOP/VDOP/TDOP/FOM/TFOM) FOF                |            |

| TSync-PCle                                                                       | 150        |

| Driver Issue: GR_GetSatData 0 0 responding with invalid five (5) digit Satellite |            |

| numbers (instead of two digits)                                                  | 152        |

| **DAGR GPS receiver ("Defense Advanced GPS Receiver" interface)                  | 154        |

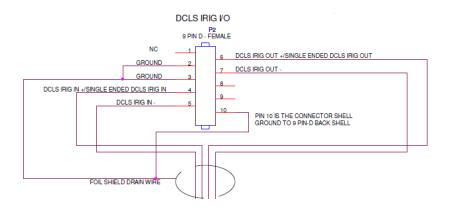

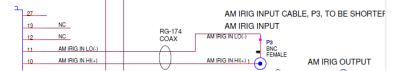

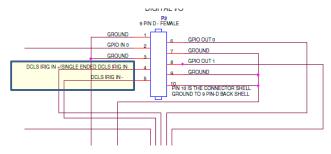

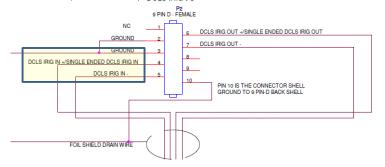

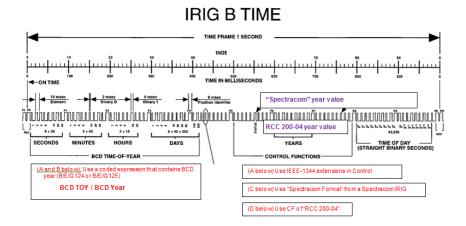

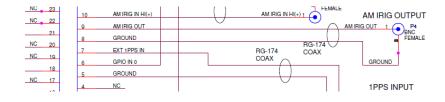

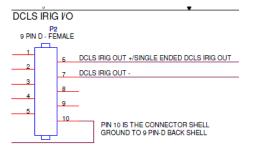

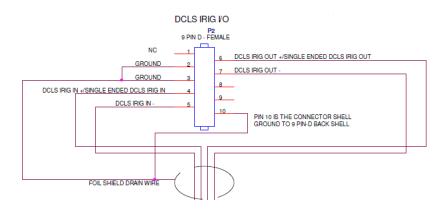

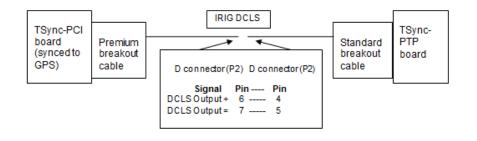

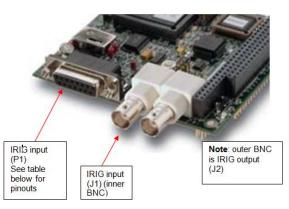

| **IRIG AM/ IRIG DCLS input synchronization                                       | 155        |

|                                                                                  | 3          |

| **IRIG cabling (such as RG-58 coax cable)                                                                                                    | 155        |

|----------------------------------------------------------------------------------------------------------------------------------------------|------------|

| API calls associated with IRIG input                                                                                                         | 156        |

| IRIG input minimum signal level requirements (from the TSync data sheet)                                                                     | 156        |

| Input impedances/input termination requirements                                                                                              | 157        |

| Accuracy to IRIG input reference:                                                                                                            | 158        |

| "Pseudo IRIG-B" timecode- IRIG plus Countdown (Count-down) / IRIG with                                                                       | 460        |

| Countdown and Countup (count-up)                                                                                                             | 160<br>172 |

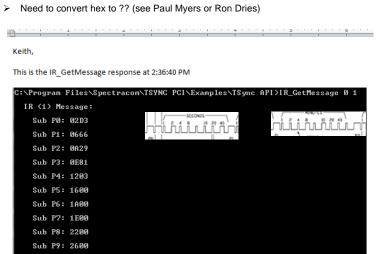

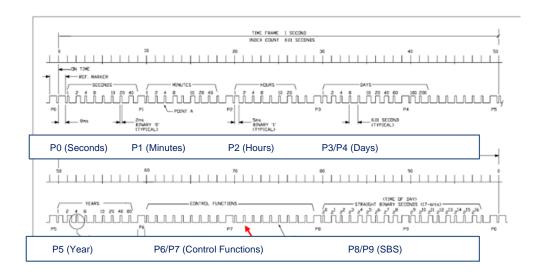

| IRIG generator providing local time input ("Local clock" via IR_SetLocal)<br>Reading raw IRIG input signal data (IR_GetMessage/IR_GetCfData) | 172        |

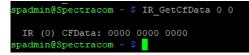

| IR GetCFData                                                                                                                                 | 174        |

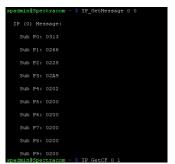

| IR GetMessage                                                                                                                                | 174        |

| *****IRIG AM and IRIG DCLS input validity (IR_GetValidity) / Troubleshooting IR                                                              |            |

| input                                                                                                                                        | 177        |

| **New Year rollover                                                                                                                          | 179        |

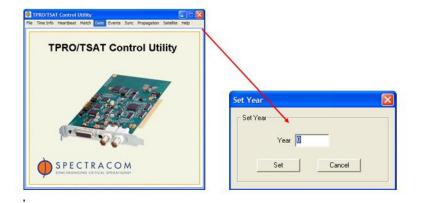

| *Setting the year value upon each TSync-PCle power-up                                                                                        | 180        |

| **IRIG input Year info                                                                                                                       | 181        |

| Desire to receive the 1344 extensions (IEEE C37.118-2005) from the IRIG input                                                                |            |

| Control Function field                                                                                                                       | 198        |

| **Troubleshooting IRIG input synchronization                                                                                                 | 200        |

| **TSYNC_DRV_CONNECTION_ERR with "IR" calls                                                                                                   | 200        |

| 201                                                                                                                                          | 200        |

| **UT1 correction factor (leap seconds)                                                                                                       | 201        |

| ***Leap Smear (Smearing the leap second instread of a one second instananio                                                                  |            |

| correction)                                                                                                                                  | 201        |

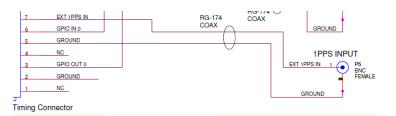

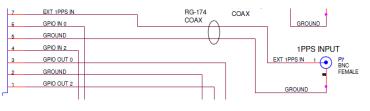

| External 1PPS" Input Reference (Self/EPP0 and Hst0/EPP0)                                                                                     | 201        |

| Troubleshooting EPP0 (external 1PPS input)                                                                                                   | 202        |

| Oscillators: Osc cal and disciplining to PPS ref / TFOM / Holdover                                                                           | 200        |

| API calls associated with the oscillator                                                                                                     | 207        |

|                                                                                                                                              |            |

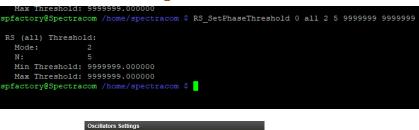

| Smart Reference Monitoring/Phase Threshold (firmware v3.4.7 and above only                                                                   | 210<br>()  |

| Sinart Reference wonitoring/r hase threshold (in hware vo.4.7 and above only                                                                 | 213        |

| Phase Error limit                                                                                                                            | 220        |

| Oscillator 10 MHz Accuracy (Oscillator accuracy when locked to a reference)                                                                  | 220        |

| Fractional Frequency Error (FFE)                                                                                                             | 221        |

| "1PPS not in Specification" / "1PPS Restored to Specification" log entries                                                                   | 226        |

| **TFOM / Max TFOM / Time Accuracies of TSync-PCle boards                                                                                     | 227        |

| Outputs                                                                                                                                      | 230        |

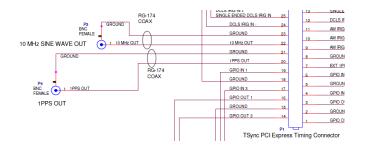

| *10MHz output                                                                                                                                | 231        |

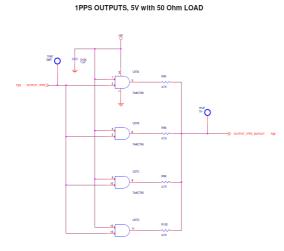

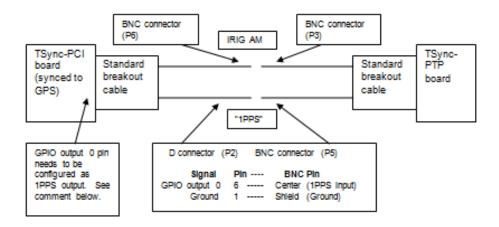

| *1PPS output                                                                                                                                 | 233        |

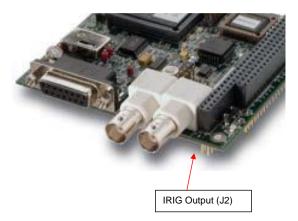

| *IRIG output                                                                                                                                 | 238        |

| Available IRIG output configuration commands (these are the "IP" calls/example                                                               |            |

| programs)                                                                                                                                    | 244        |

| r                                                                                                                                            | 4          |

|                                                                                                                                              | 4          |

| ***desire to output IEEE-1344 extensions in CF field (includes year info)            | 247        |

|--------------------------------------------------------------------------------------|------------|

| **Time output (Time reads)                                                           | 252        |

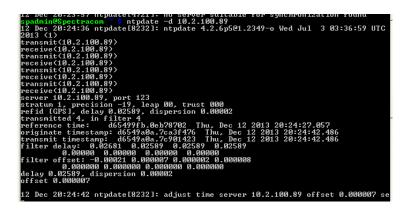

| ****Time reads (used by NTP for linux sync)                                          | 252        |

| ****Issues with Time output                                                          | 252        |

| Logs and Alarms (Holdover/Time Sync/Frequency Error/Freerun/PPS                      |            |

| Specification/Reference Change, etc)                                                 | 253        |

| ****Enabling alarms                                                                  | 253        |

| ****LS_GetAlarm call / example program                                               | 253        |

| ****Remote alarm indications/alert notification                                      | 256        |

| **PTP Master mode (PTP output)                                                       | 257        |

| Logs/log Messages                                                                    | 257        |

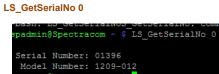

| Tsync-PCle's Model and Serial Number                                                 | 258        |

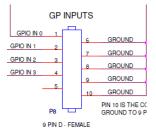

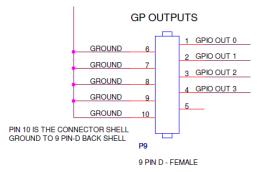

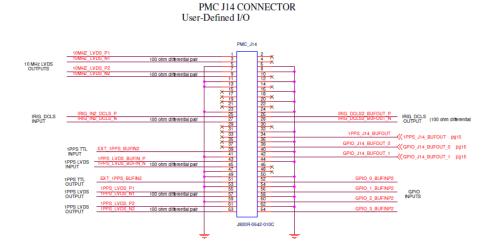

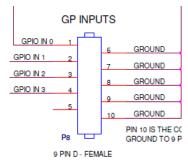

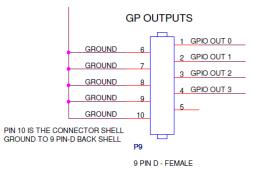

| GPIO (General Purpose Input Output) pins                                             | 260        |

| **GPI pins (General Purpose Inputs- "GPI")                                           | 260        |

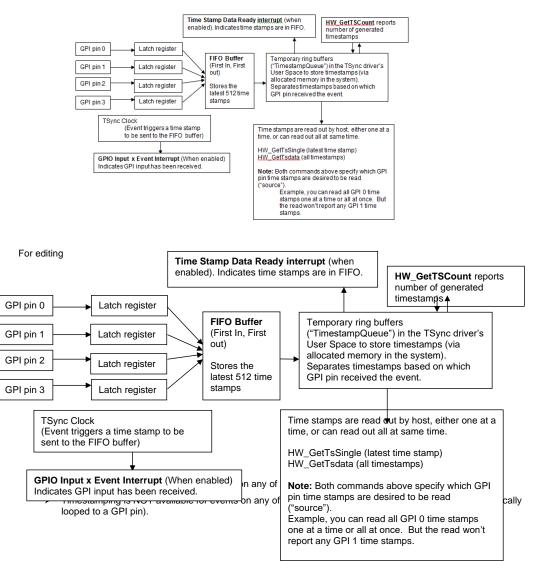

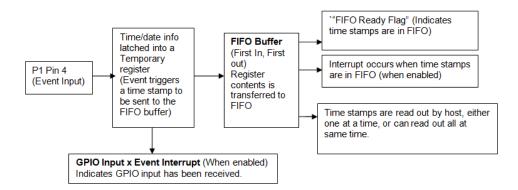

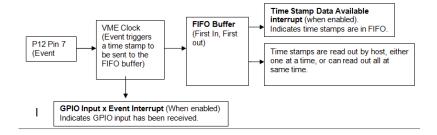

| Time tag (timestamping/Time Stamping/Timetag) / External Event Input                 | 262        |

| **FIFO Buffer info (First In, First out)                                             | 267        |

| **GPO pins (General Purpose Outputs- "GPO")                                          | 271        |

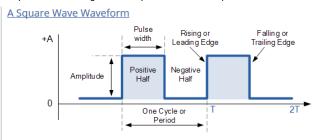

| B) Square Wave mode                                                                  | 279        |

| **Desire to convert the GPO outputs to 1PPS outputs                                  | 281        |

| Desire to convert the GPO outputs to 1PPM outputs                                    | 281        |

| C) Match Time mode                                                                   | 282        |

| DRIVERS (Windows Linux Solaris)                                                      | 286        |

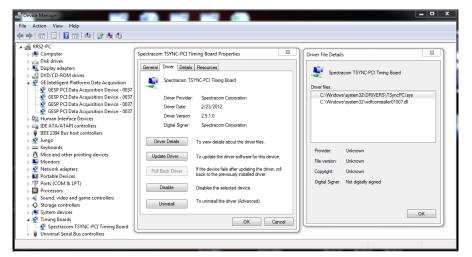

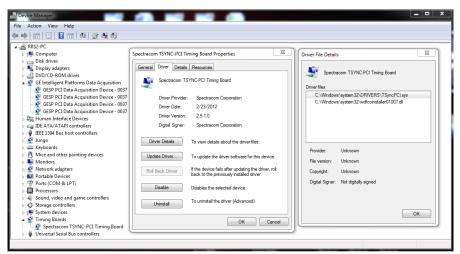

| TSync-PCle Driver version/ driver updates                                            | 287        |

| Open-source software/EULA software license for Spectracom TSync and                  | 201        |

| TPRO/TSAT drivers                                                                    | 288        |

|                                                                                      | 200<br>290 |

| Board handle and device index, index (Instance) Number                               | 290        |

| VxWorks, Matlab Simulink or other custom drivers not available from us               | 291        |

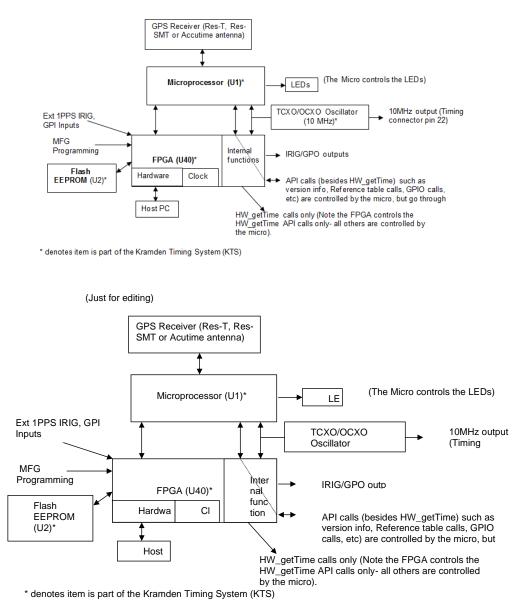

| Host Interface Protocol                                                              | -          |

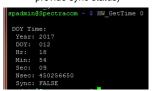

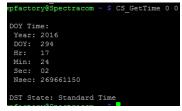

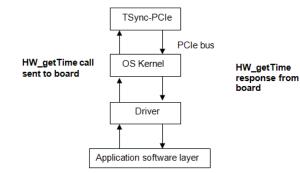

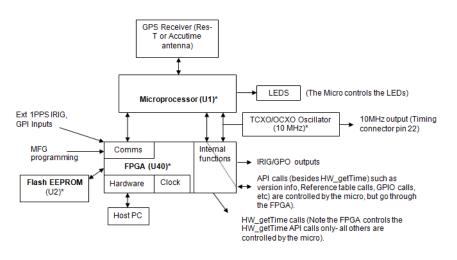

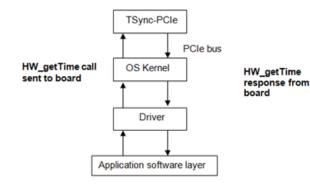

| HW commands (such as HW_GetTime)                                                     | 293        |

| ***static (tsync.lib files) and dynamic (tsync.dll files) library files / .lib files | 000        |

| (libtsync.so versus libtsync.a)                                                      | 296        |

| Compiling Customer's application software                                            | 298        |

| C# (called "C Sharp", "Managed Code C #" or "Managed Code C Sharp")                  | 298        |

| **TROUBLESHOOTING TSync boards                                                       | 299        |

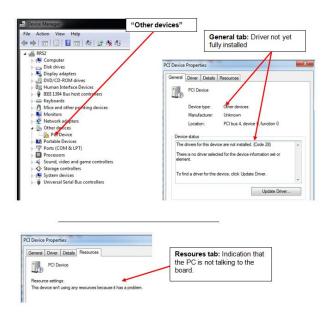

| ****TSync-PCle board doesn't appear to be operational after install                  | 299        |

| TSYNC_open() and TSYNC_close() API calls                                             | 302        |

| TSYNC_COMM_ERR                                                                       | 303        |

| TSync compatibility with Matlab programming language                                 | 304        |

| TSync Windows Driver/ Visual Studio                                                  | 306        |

| Paths on PC to TSync driver and example programs (C:\)                               | 306        |

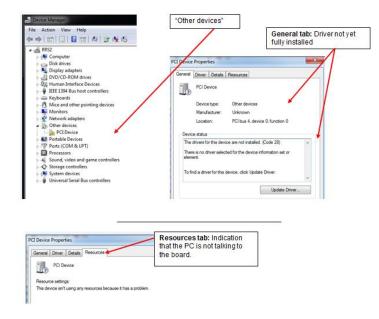

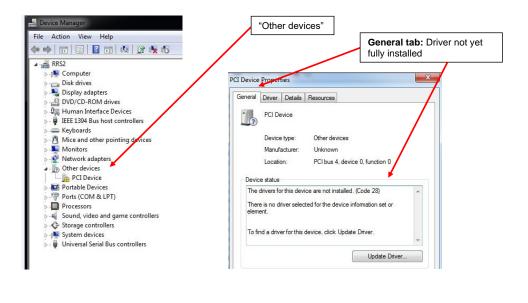

| TROUBLESHOOTING WINDOWS DRIVER INSTALL                                               | 307        |

| **Windows Driver compatibility/install issues/conflicts with other PCIe boards       | 309        |

| <ul> <li>Base Address Register (BAR) fix: Windows driver installs fine, but Control Uti has problem interfacing with the TSync-PCle board</li> <li>Windows driver v3.2.1 and above install issues due to the currently installed version off Visual C++ Redistributable installed on PC being newer than the version provided with the Windows driver (and don't want to remove currently installed version provided with the Windows driver (and don't want to remove currently installed version provided with the Windows driver (and don't want to remove currently installed version provided with the Windows driver (and don't want to remove currently installed version provided with the Windows driver (and don't want to remove currently installed version provided with the Windows driver (and don't want to remove currently installed version provided with the Windows driver (and don't want to remove currently installed version provided with the Windows driver (and don't want to remove currently installed version provided with the Windows driver (and don't want to remove currently installed version provided with the Windows driver (and don't want to remove currently installed version provided with the Windows driver (and don't want to remove currently installed version provided with the Windows driver (and don't want to remove currently installed version provided with the Windows driver (and don't want to remove currently installed version provided with the Windows driver (and don't want to remove currently installed version provided with the Windows driver (and don't want to remove currently installed version provided with the Windows driver (and don't want to remove currently version provided with the Windows driver (and don't want to remove currently version provided with the Windows driver (and don't want to remove currently version provided with the Windows driver (and don't want to remove currently version provided with the Windows driver (and don't want to remove currently version provided with the Windows driver (and don't wan</li></ul> | 314<br>Э |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| version to install the driver)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 316      |

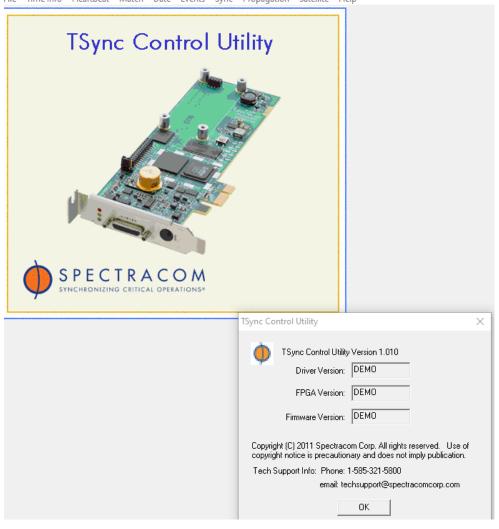

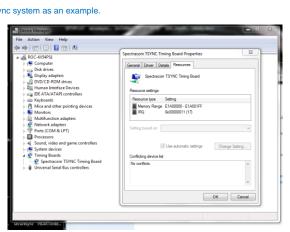

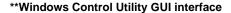

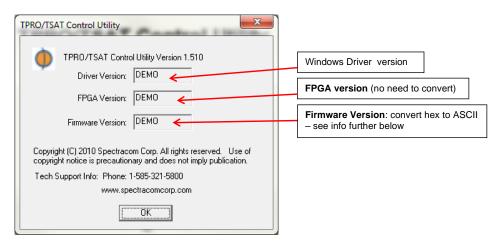

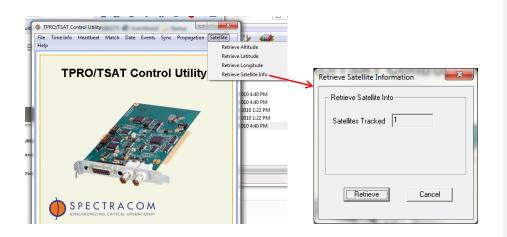

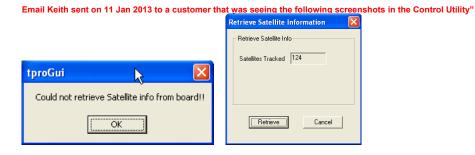

| **Windows Control Utility GUI interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 321      |

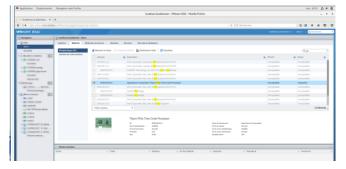

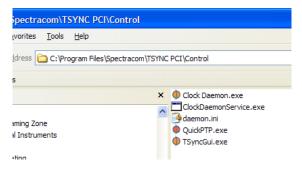

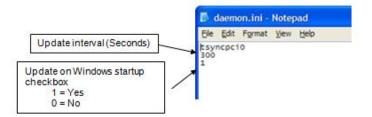

| Syncing Windows using a TSync Timing board (Clock Daemon/TSync Time<br>Provider)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 321      |

| Syncing TSync board to the Windows OS (via Host Reference)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 323      |

| Using TSync in Virtual Machines/VMs/Virtual environments (such as VMware/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ESX      |

| and ESXI, Hyper-V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 326      |

| **Windows Hyper-V (ESXI hypervisor) and other Virtual machines (VMs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 327      |

| Inherent issues with NTP Stability in VMs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 331      |

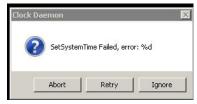

| **B) Clock Daemon program / Clock Daemon service (for all timing boards) an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

| bit Windows                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 332      |

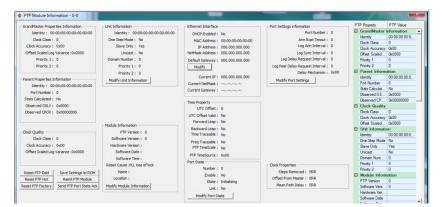

| TSync "QuickPTP Viewer / "TSync Viewer" GUI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 342      |

| Windows with UEFI Secure Boot (Trusted Boot)/digital Signature requirement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| .net Frame work for TSync-PCle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 348      |

| Visual Studio (VS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 349      |

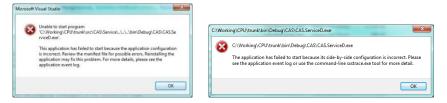

| **CAS.Service and Side-by-Side errors (Side by Side Configuration)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 354      |

| Labview driver/Labview wrapper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 355      |

| Linux driver specific                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 357      |

| Linux Debian Stretch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 358      |

| **Updating the Linux driver (Uninstalling a previous version Linux driver and installing a newer version)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 360      |

| 32 Bit application software on our 64 bit TSync driver (compat_ioctl function)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 362      |

| ***static and dynamic library files / .lib files (libtsync.so versus libtsync.a)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 363      |

| Example programs for the Linux driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 364      |

| Multi-core / Multi-thread applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 365      |

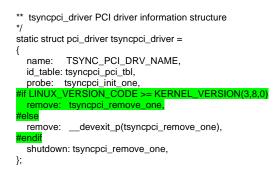

| **TROUBLESHOOTING linux driver/driver compile errrors:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 366      |